2018年,中国组承担的ATLAS Phase I升级中探测器端盖部分的Muon sTGC谱仪读出电子学取得突破性进展,前端读出电子学系统完成了工程设计,并通过了由CERN组织的工程设计审查(Final Design Review,FDR)。

ATLAS 探测器正在进行Phase I阶段的升级工作,端盖部分的Muon 谱仪使用了超高精度位置分辨的sTGC气体探测器,每块读出电子学板的原始数据量为6Gbps,触发数据量为4.8Gbps,整个系统设计没有现成的芯片和电路可供选择。

韩良教授、金革教授、李锋博士组成的研究组完成了单个读出模块512路的电子学读出设计,其噪声水平小于0.6mV,是目前国际上高能物理实验中通道密度最高、灵敏度最高、噪声水平最低的探测器读出电子学。

sTGC前端读出电子学的工程板经过一系列测试结果表明:前端读出电子学系统能够与各配接电子学系统完美配合,实现了从顶层Felix系统到底层的前端ASIC芯片的准确配置、探测器信号的原始数据及触发数据的准确读出,以及跟其他触发系统一起实现了完整的触发链路测试。整个电子学系统包含768套电子学板(不含20%的工程备份),多达33万通道,将于2019年开始批量生产,并在2019年底完成工程安装。

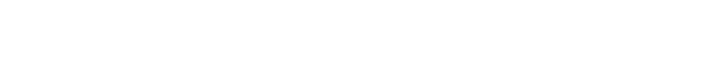

pFEB v2.3a电路板正面(尺寸165×60mm,约1/6 A4纸大小)

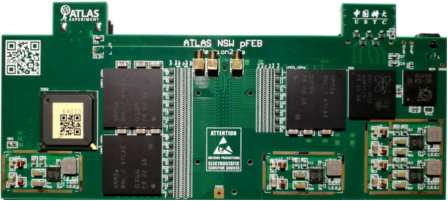

pFEB v2.3a电路板背面

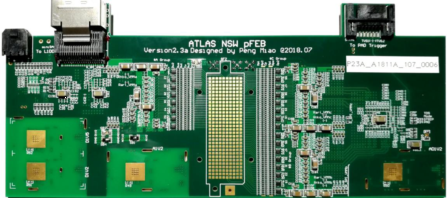

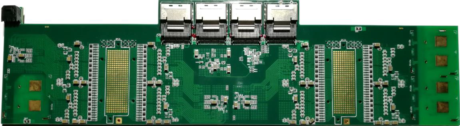

sFEB v2.3a Type A电路板正面(尺寸270×60mm,约1/4 A4纸大小)

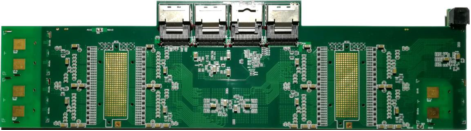

sFEB v2.3a Type A电路板背面

sFEB v2.3a Type B电路板正面(尺寸270×60mm,约1/4 A4纸大小)

sFEB v2.3a Type B电路板背面

科大提交给Muon合作组的FDR报告