(1) SOI像素探测器

SOI像素探测器有全耗尽的高阻灵敏衬底,使其在X射线和带电粒子探测中均有很好的粒子-信号转换能力:对于X射线体现在量子效率,对带电粒子则体现在原初电离电荷量。近年来SOI像素探测器技术的研发工作也一直沿着这两条线平行开展。

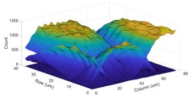

在X射线应用研发工作方面,计数型SOI像素探测器芯片CNPTEG1面向低能(2-12 keV)X射线成像,追求低噪声和高分辨。但随着像素缩小到50μm时,电荷共享效应变得越来越明显,造成像素边界的响应一致性变差。因此实验室与KEK合作设计的CNPTEG1引入了电荷共享判选机制,提高像素边界的效率一致性。利用KEK/PF BL-14A提供的微聚焦光斑扫描了4个相邻像素的边界(见下图),通过像素内的信号比较电路准确判断每一个光子应该属于哪个像素。结果表明这种设计能够有效避免漏计数或者多次计数。这项工作对于进一步提高计数型像素探测器的空间分辨至关重要,发表于同行评议期刊JINST (L. Song et al 2020 JINST 15 P01037)。

在带电粒子应用方面,CPV系列芯片的设计是面向未来高能正负电子对撞机顶点探测器需求。在前两个版本中,验证了16μm像素尺寸可以达到2.8μm的空间分辨率,但是阈值一致性有待改善。因此CPV3的设计中进行了有针对性的优化。

(a) (b) (c)

(d) (e)

计数型SOI像素探测器芯片CNPTEG1:(a) 正六边形像素; (b) 探测器芯片; (c) 同步辐射束流测试; (d) 边界处各像素的计数值; (e) 相邻像素求和后的响应一致性.

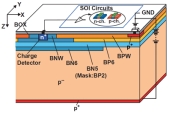

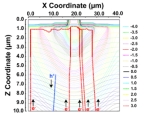

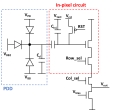

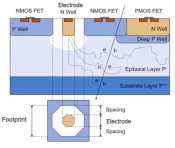

一方面,sensor diode采用了新一代PDD (Partially Depleted Diode) 结构。这种结构在抑制si-sio2界面处的暗电流和降低结电容方面取得了良好的效果,同时又提高了像素边界的共享电荷的收集效率。增加的共享电荷在电路更容易被测量,从而降低对阈值甄别的要求。

(a) (b)

Partially Depleted Diode结构 (本图引自Sensors 2018, 18, 1789): (a) 叠层示意图; (b) 耗尽区电场分布与电子漂移路径

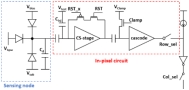

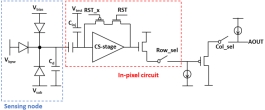

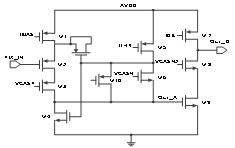

另一方面,像素电路(下图)优化了共源放大器(电压增益13)的输入管和负载管尺寸,以降低Fixed Pattern Noise (FPN);第二级的共源共栅作为比较器,两级之间交流耦合,通过Vclamp实现相关双采样和施加阈值电压;增加了专用的3-Transistor结构和模拟输出结构来全面测试Sensor和放大器特性。这些优化设计工作已在HSTD12国际会议上报告(Zhigang Wu etc., A novel SOI-PDD design for the CEPC vertex detector, HSTD12, Hiroshima, Dec 14-18, 2019)。

(a) (b)

(c) (d)

顶点探测器像素芯片CPV3的几种像素内电路:(a) 共源放大器作为输入级; (b) 共源共栅放大器作为输入级; (c) 放大器测试用的模拟输出; (d) Sensor测试用的3-Transisotr电路

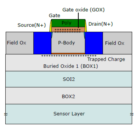

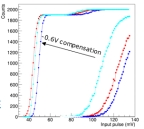

SOI像素探测器的总电离剂量(TID)辐照损伤主要源自埋氧层(Buried Oxide layer, BOX)产生的空间正电荷。通过在SOI2层施加负偏压可以补偿空间正电荷造成的阈值偏移。这一概念在计数型SOI像素探测器芯片CPIXTEG3b上得到了验证。下图显示经过100 krad辐照后畸变的特征s-curve曲线可被SOI2层施加-0.6V的偏压完全修正。SOI2的负电压被ESD保护电路钳制在-0.6V以内,但如果设法进一步增加SOI2的负偏压,对更高剂量的有效补偿也应该是可行的。这部分工作相关的文章已被同行评议期刊JINST接收(Longlong Song etc., Total ionization dose effects and compensation in a counting type double SOI pixel sensor, accepted by JINST on Feb. 28, 2020)。

(a) (b) (c)

X射线辐照的计数型SOI像素探测器芯片CPIXTEG3b: (a) DSOI2的叠层结构; (b) ROI #1 = 10 krad, ROI #1 = 100 krad, ROI #1 = 300 krad; (c) 100 krad辐照后畸变的特征s-curve曲线可被SOI2层上的负偏压修正。

(2) CMOS像素探测器芯片研制

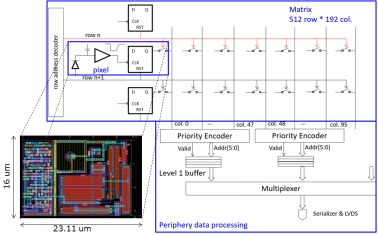

CMOS像素探测器采用高阻外延层的四阱工艺,漏电流低,结电容小,适合于低噪声应用。面向未来高能正负电子对撞机顶点探测器的高精度低功耗性能要求,CMOS像素探测器芯片JadePix3主要在读出架构上进行优化,而其前续版本对Sensing diode和模拟前端已经进行了细致研究。

JadePix3的像素按列组织读出:列级采用Rolling shutter模式;列端级(End-of-Column)则采用优先级编码和异步复位(Priority Encoder and Asynchronous Reset, AERD)模块将有击中的列依次读出和复位,其工作频率是行扫描频率的16倍。这种架构将地址编码放在像素阵列外实现,从而能够大幅度缩小像素尺寸。最终设计结果显示,像素尺寸可以缩小到16 μm×23.11μm,平均功耗估计在50 mW/cm2左右,读出速度为200 ns/行或者100 μs/帧(假设全尺寸芯片512行)。该芯片包括完备的外围功能模块,DAC,数据缓存,并串转换和高速数据传输。这部分工作已在HSTD12国际会议上报告(Yunpeng Lu, Development of high resolution low power CMOS pixel sensor for the CEPC vertex detector, oral, HSTD12, Hiroshima, Dec 14-18, 2019)。

JadePix3的读出架构

(a) (b)

CMOS像素探测器: (a) Sensing diode; (b) 模拟前端电路

CMOS像素探测器系列芯片“TaichuPix”的目标是研制出具有空间分辨3~5微米、抗辐照(总电离剂量高于1MRad),同时具有低物质量的大面积芯片。芯片研发由高能所主导,联合4家合作单位共同研发。TaichuPix-1采用TowerJazz CIS 0.18 µm工艺,针对最终研制探测器原型样机的需求,设计了包括像素阵列、阵列外围读出电路、高速串行数据传输、低压降稳压器、DAC等功能模块。TaichuPix-1芯片布局及功能与最终版TaichuPix芯片完全一致,其结构示意图和芯片照片如下图所示,最终版芯片将包含512行×1024列像素单元,并减薄至50 微米。TaichuPix-1的像素尺寸为25μm×25μm,对击中信号可实现25 ns的时间分辨精度,并且兼容最高3.84 Gb/s的击中率。目前TaichuPix-1的初步测试结果证实阵列外围读出电路和串行数据传输模块功能正常,像素阵列及其他模块的测试正在进行中。2019年,研发团队在国际会议HSTD上报告此芯片的设计(Y.ZHANG et al., Fast in-pixel readout for a CMOS pixel sensor prototype developed for the CEPC vertex detector, Poster, HSTD12, Dec. 14-28, 2019),并发表研究论文(T.Wu et al., A full functional Monolithic Active Pixel Sensor prototype for the CEPC vertex detector, 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS) proceedings, Nov. 2019)。

TaichuPix-1像素芯片结构示意图(左)和芯片照片(右)